En esta tercera entrega continuamos mostrando las patentes que tienen concedidas actualmente en España la multinacional de origen californiano creada por el ya fallecido Steve Jobs.

Mostramos 4 nuevas patentes de las 16 concedidas actualmente en España bajo la titularidad de Apple Inc. Estas patentes tienen origen norteamericano y fueron concedidas en la oficina europea de patentes y son fruto de su validación en España en forma de traducción al español de esta concesión, en ocasiones con un cierto exceso de literalidad.

Como en las dos partes anteriores se incluye para cada patente:

- una figura,

- el titulo de la patente y

- un resumen de su contenido.

Además se facilita el acceso al contenido de la memoria patente completa en español.

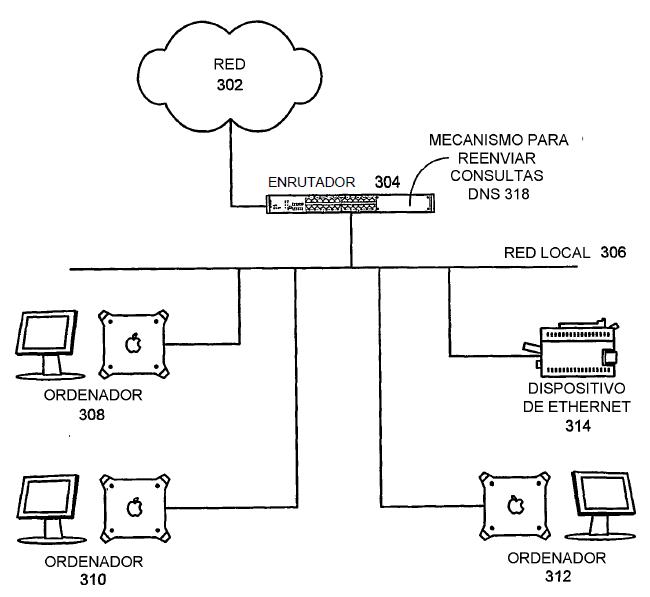

DISTRIBUCIÓN SEGURA DE CONTENIDO UTILIZANDO CLAVES DE DESCIFRADO:

Esta invención se refiere a la distribución de contenido usando un sistema criptográfico y, más específicamente, a la gestión de claves.

Esta invención se refiere a la distribución de contenido usando un sistema criptográfico y, más específicamente, a la gestión de claves.

En una técnica de cifrado en bloque bien conocida, un mensaje específico, en lugar de ser cifrado usando una única clave, se fragmenta, en cambio, en un cierto número de partes, y cada parte se cifra individualmente. Sin embargo, en los típicos cifrados anteriores en bloque, se usa la misma clave para cada bloque del mensaje. Si bien esto es satisfactorio para los enfoques tradicionales de cifrado, donde habitualmente cada mensaje se envía solamente una vez, no es adecuado para la situación actual, donde un fragmento específico de contenido puede distribuirse a decenas o cientos de miles de usuarios con la misma clave.

Por lo tanto, según esta divulgación, cada fragmento de contenido cifrado, cuando se distribuye, está acompañado por un valor inicial de clave.

Con fines de descifrar el contenido, se genera una primera clave a partir del valor inicial de clave, usando una función (predeterminada) conocida. El contenido, para los fines del cifrado (y del descifrado posterior), se fragmenta en una pluralidad de partes o bloques. Estas no necesariamente deben ser de igual longitud.

La primera clave generada a partir del valor inicial de clave se usa para descifrar la primera parte o bloque del mensaje.

Sin embargo, esa clave no es útil para los bloques restantes. En lugar de que se use solamente una clave para descifrar el fragmento entero de contenido (mensaje), un típico fragmento de contenido (canción o vídeo, por ejemplo) tiene múltiples claves.

Esto hace que el ataque de diccionario anteriormente descrito sea muy insatisfactorio, ya que los piratas, en lugar de publicar solamente una única clave o valor de clave para cada fragmento de contenido, deben publicar un gran número de ellas y, además, dado que la longitud de los bloques puede variar entre canción y canción, o incluso dentro de una canción (fragmento de contenido), incluso la disponibilidad de la lista entera de claves no proporciona un descifrado adecuado, ya que también hay que conocer, con fines de descifrado, una longitud de cada bloque.

Acceso a la memoria completa: ES-2373131_T3

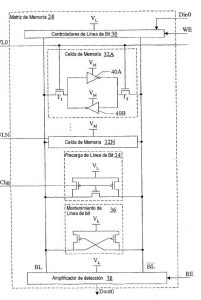

CIRCUITO INTEGRADO CON TENSIÓN DE ALIMENTACIÓN INDEPENDIENTE PARA LA MEMORIA QUE ES DIFERENTE DE LA TENSIÓN DE ALIMENTACIÓN DEL CIRCUITO LÓGICO:

En las reivindicaciones se definen un circuito integrado y un procedimiento que conforman los aspectos de la invención, donde las reivindicaciones independientes son:

En las reivindicaciones se definen un circuito integrado y un procedimiento que conforman los aspectos de la invención, donde las reivindicaciones independientes son:

1. Un circuito integrado (10), que comprende:

por lo menos un circuito lógico (12) alimentado por una primera tensión de alimentación (VL) recibida en una primera entrada al circuito integrado; y

por lo menos un circuito de memoria (14) acoplado al circuito lógico y alimentado por una segunda tensión de alimentación (VM) recibida en una segunda entrada en el circuito integrado, y en el que el circuito de memoria se configura para ser leído y escrito en respuesta al circuito lógico incluso si la primera tensión de alimentación es menor que la segunda tensión de alimentación y en el que el circuito de memoria comprende por lo menos una matriz de memoria (24),

en el que la matriz de memoria comprende una pluralidad de celdas de memoria (32) que son alimentadas continuamente por la segunda tensión de alimentación durante el uso, el circuito de memoria comprende un circuito de control de línea de palabra (22) alimentado por la segunda tensión de alimentación, una primera celda de memoria (32A) de la pluralidad de celdas de memoria (32A-32N) se acopla a una línea de palabra, recibiendo la línea de palabra la segunda tensión desde el circuito de control de línea de palabra (22) para activar la primera celda de memoria para el acceso, la primera celda de memoria se acopla a un par de líneas de bit, el circuito de memoria comprende adicionalmente un circuito de precarga de línea de bit (34) configurado para precargar el par de líneas de bit para prepararse para la lectura, y caracterizado porque el circuito de precarga de línea de bit es alimentado por la primera tensión de alimentación para precargar las líneas de bit a la primera tensión de alimentación.

11. Un procedimiento que comprende, en un circuito integrado (10):

la lectura por un circuito lógico (12) de una celda de memoria (32A), siendo alimentado el circuito lógico por una primera tensión de alimentación (VL) recibida en una primera entrada en el circuito integrado; y la respuesta por la celda de memoria a la lectura que utiliza señales que son referenciadas a la primera tensión de alimentación, en el que la celda de memoria es alimentada con una segunda tensión de alimentación (VM) que es mayor que la primera tensión de alimentación durante el uso, y en el que la segunda tensión de alimentación es recibida en una segunda entrada en el circuito integrado, y en el que el circuito de memoria comprende por lo menos una matriz de memoria (24),

en el que la matriz de memoria comprende una pluralidad de celdas de memoria (32A-32N) que son alimentadas continuamente por la segunda tensión de alimentación durante el uso, el circuito de memoria comprende un circuito de control de línea de palabra (22) alimentado por la segunda tensión de alimentación, la celda de memoria (32) se acopla a una línea de palabra, recibiendo la línea de palabra la segunda tensión del circuito de control de línea de palabra (22) para activar la celda de memoria para el acceso, la primera celda de memoria se acopla a un par de líneas de bit, el circuito de memoria comprende adicionalmente un circuito de precarga de línea de bit (34) configurado para precargar el par de líneas de bit para prepararse para la lectura, y, caracterizado porque el circuito de precarga de línea de bit es alimentado por la primera tensión de alimentación para precargar las líneas de bit a la primera tensión de alimentación.

Acceso a la memoria completa: ES-2370338_T3

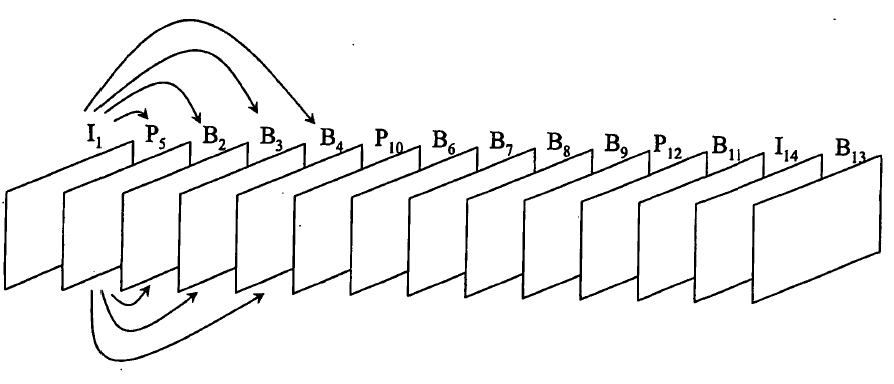

PROCEDIMIENTO Y APARATO DE ESPECIFICACIÓN DE TEMPORIZACIÓN ENTRE IMÁGENES DE PRECISIÓN VARIABLE PARA LA CODIFICACIÓN DE VÍDEO DIGITAL:

La invención se refiere al campo de los sistemas de compresión multimedia. En particular, la presente invención divulga procedimientos y sistemas para especificar temporización entre imágenes de precisión variable.

Se revela un procedimiento y aparato para la especificación de temporización entre imágenes de precisión variable para la codificación de vídeo digital. Específicamente, la presente invención divulga un sistema que permite que la temporización relativa de imágenes de vídeo contiguas se codifique de manera muy eficaz. En una realización, se determina la diferencia de tiempo de exhibición entre una imagen de vídeo actual y una imagen de vídeo contigua. La diferencia de tiempo de exhibición se codifica luego en una representación digital de la imagen de vídeo. En una realización preferida, la imagen de vídeo contigua es la imagen almacenada más recientemente transmitida.

Para la eficacia de la codificación, la diferencia de tiempo de exhibición puede codificarse usando un sistema de codificación de longitud variable, o codificación aritmética. En una realización alternativa, la diferencia de tiempo de exhibición se codifica como una potencia de dos, a fin de reducir el número de bits transmitidos.

Otros objetos, características y ventajas de la presente invención serán evidentes a partir de los dibujos acompañantes y de la siguiente descripción detallada.

Acceso a la memoria completa: ES-2355816_T3

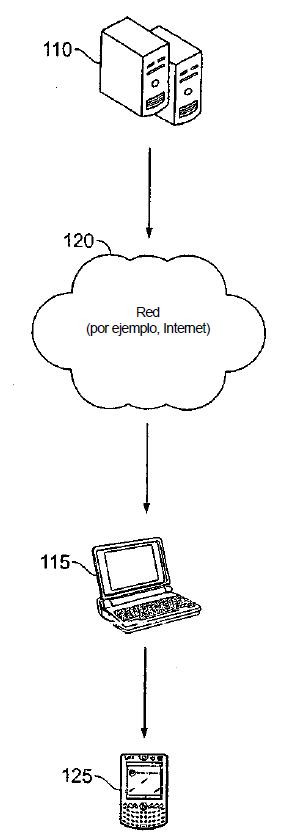

SISTEMA DE CIRCUITOS DE COMUNICACIONES INALÁMBRICAS CON CAPACIDAD DE RECEPCIÓN SIMULTÁNEAS PARA DISPOSITIVOS ELECTRÓNICOS DE MANO:

Según una forma de realización de la presente invención, se proporciona un dispositivo electrónico de mano con sistema de circuitos de comunicaciones inalámbricas. El dispositivo electrónico de mano puede tener una funcionalidad de teléfono móvil, reproductor de música, o de ordenador de mano. El sistema de circuitos de comunicaciones inalámbricas pueden tener múltiples transceptores que comparten una antena.

Con una configuración adecuada, el sistema de circuitos de comunicaciones inalámbricas tiene unos transceptores primero y segundo. El primer transceptor puede ser, por ejemplo, un circuito integrado de transceptor de red de área local inalámbrica (WLAN) que gestiona el tráfico IEEE 802.11. El segundo transceptor puede ser un transceptor Bluetooth. El primer transceptor y el segundo transceptor pueden operar en una banda de frecuencia común (p. ej., una banda de frecuencias de comunicaciones de 2,4 GHz).

El sistema de circuitos de comunicaciones inalámbricas puede tener un acoplador de radiofrecuencia y un sistema de circuitos de conmutación. Cuando se desea recibir al mismo tiempo señales de radiofrecuencia entrantes de la antena con el primer transceptor y el segundo transceptor, se utiliza el acoplador para dividir las señales de radiofrecuencia entrantes en unas versiones de potencia reducida idénticas primera y segunda de las señales entrantes de radiofrecuencia. Estas señales se proporcionan simultáneamente a los transceptores primero y segundo en paralelo.

Las versiones primera y segunda de las señales entrantes que son producidas por el acoplador pueden tener la misma potencia de señal o pueden tener potencias de señal diferentes. Con una configuración adecuada, el acoplador es asimétrico, de manera que la señal que se desvía a los circuitos transceptores de red de área local inalámbrica tiene una potencia relativamente mayor que la señal que se desvía al transceptor Bluetooth.

Cuando se desea transmitir datos WLAN, el sistema de circuitos de conmutación se ajusta adecuadamente y el transceptor WLAN se activa mientras que el transceptor Bluetooth se inactiva. Puede utilizarse un amplificador de potencia para amplificar los datos de salida WLAN transmitidos.

Cuando se desea utilizar el transceptor Bluetooth sin utilizar el transceptor WLAN, el transceptor WLAN se pone en un estado inactivo. Cuando el transceptor WLAN está inactivo, no es necesario recibir datos simultáneamente con los circuitos WLAN y Bluetooth. Como resultado, el sistema de circuitos de conmutación puede ajustarse para circunvalar el acoplador. Con el acoplador circunvalado, pueden transmitirse datos Bluetooth o pueden recibirse datos Bluetooth. Cuando se reciben datos Bluetooth de esta manera, existe una potencia de señal relativamente mayor, porque se evita la pérdida de inserción del acoplador. Si se desea, puede ponerse un amplificador de entrada aguas arriba del acoplador para compensar la pérdida de inserción del acoplador.

Las características adicionales de la invención, su naturaleza y diversas ventajas se pondrán de manifiesto a partir de los dibujos adjuntos y la siguiente descripción detallada de las formas de realización preferentes

Acceso a la memoria completa: ES-2363818_T3

La próxima entrega de esta serie de artículos se publicara el próximo lunes 19 de marzo de 2012.